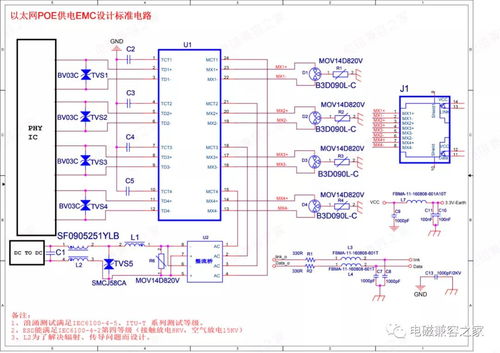

在軟件開發(fā)領(lǐng)域,尤其是在嵌入式系統(tǒng)、物聯(lián)網(wǎng)設(shè)備和工業(yè)控制等方向,電磁兼容性(EMC)設(shè)計(jì)不僅關(guān)乎硬件電路的穩(wěn)定性,也深刻影響著軟件運(yùn)行的可靠性與性能。合理運(yùn)用電磁兼容設(shè)計(jì)標(biāo)準(zhǔn)中的參考電路,并將其與軟件開發(fā)流程緊密結(jié)合,已成為提升產(chǎn)品整體質(zhì)量的關(guān)鍵。本文將探討如何將這38個(gè)標(biāo)準(zhǔn)參考電路有效地融入軟件開發(fā)周期,實(shí)現(xiàn)軟硬件的協(xié)同優(yōu)化。

一、電磁兼容設(shè)計(jì)與軟件開發(fā)的交匯點(diǎn)

電磁兼容問題常表現(xiàn)為信號(hào)干擾、數(shù)據(jù)錯(cuò)誤或系統(tǒng)復(fù)位等,這些現(xiàn)象往往需要通過軟件手段進(jìn)行檢測(cè)、補(bǔ)償或容錯(cuò)處理。例如,參考電路中涉及的濾波、屏蔽和接地設(shè)計(jì),直接影響著軟件采集數(shù)據(jù)的精度和通信協(xié)議的穩(wěn)定性。開發(fā)人員需理解這些電路的工作原理,才能在軟件層面設(shè)計(jì)相應(yīng)的抗干擾算法,如數(shù)字濾波、錯(cuò)誤校驗(yàn)與重傳機(jī)制。

二、參考電路在軟件開發(fā)各階段的應(yīng)用

1. 需求分析與規(guī)劃階段

根據(jù)38個(gè)參考電路的特點(diǎn)(如針對(duì)電源噪聲、射頻干擾或靜電放電的防護(hù)電路),明確軟件需處理的異常類型。制定軟件需求規(guī)格書時(shí),應(yīng)包含對(duì)電磁干擾的容忍度指標(biāo),并規(guī)劃相應(yīng)的軟件測(cè)試用例。

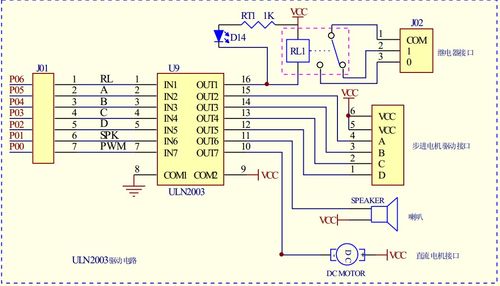

2. 架構(gòu)設(shè)計(jì)與編碼階段

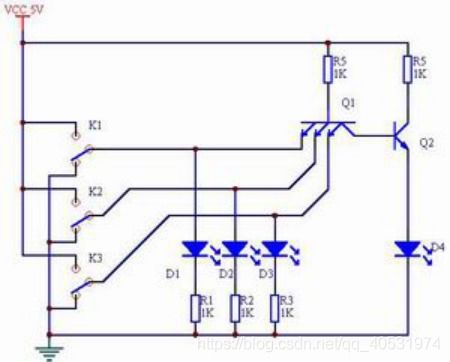

參考電路中的硬件濾波特性可指導(dǎo)軟件中采樣頻率和數(shù)字濾波器參數(shù)的選擇。例如,對(duì)于采用RC濾波的輸入電路,軟件可結(jié)合過采樣技術(shù)以提升信噪比。針對(duì)易受干擾的通信接口(如UART、I2C),參考電路的屏蔽與隔離設(shè)計(jì)提醒開發(fā)人員增加軟件層面的超時(shí)重試和幀校驗(yàn)功能。

3. 集成測(cè)試與驗(yàn)證階段

利用參考電路構(gòu)建的測(cè)試環(huán)境,模擬各類電磁干擾場(chǎng)景(如脈沖群、浪涌),驗(yàn)證軟件在極端條件下的健壯性。自動(dòng)化測(cè)試腳本可集成這些場(chǎng)景,持續(xù)監(jiān)測(cè)軟件的誤碼率、響應(yīng)時(shí)間等關(guān)鍵指標(biāo)。

4. 維護(hù)與優(yōu)化階段

通過軟件日志記錄系統(tǒng)在真實(shí)環(huán)境中遇到的干擾事件,與參考電路的預(yù)期防護(hù)效果進(jìn)行對(duì)比分析。此數(shù)據(jù)可反饋至硬件優(yōu)化,或用于迭代軟件的錯(cuò)誤處理邏輯,形成閉環(huán)改進(jìn)。

三、實(shí)踐建議與工具支持

- 建立軟硬件協(xié)同設(shè)計(jì)流程:鼓勵(lì)軟件開發(fā)人員早期參與電路評(píng)審,理解關(guān)鍵EMC風(fēng)險(xiǎn)點(diǎn)。使用模型化工具(如Simulink)進(jìn)行聯(lián)合仿真,評(píng)估軟件算法在干擾環(huán)境下的表現(xiàn)。

- 開發(fā)專用軟件庫(kù):將常見的抗干擾處理(如CRC校驗(yàn)、看門狗管理、信號(hào)去抖)封裝為可重用模塊,并附上對(duì)應(yīng)的參考電路應(yīng)用說明,提升團(tuán)隊(duì)效率。

- 持續(xù)教育與案例分享:定期組織專題研討,分析這38個(gè)參考電路在實(shí)際項(xiàng)目中的成功應(yīng)用案例,強(qiáng)化團(tuán)隊(duì)的EMC意識(shí)。

###

電磁兼容設(shè)計(jì)不僅是硬件工程師的職責(zé),更是軟件開發(fā)中不可忽視的一環(huán)。通過深入理解并靈活運(yùn)用38個(gè)標(biāo)準(zhǔn)參考電路,軟件團(tuán)隊(duì)能夠提前規(guī)避潛在風(fēng)險(xiǎn),打造出更穩(wěn)定、可靠的產(chǎn)品。在日益復(fù)雜的電子系統(tǒng)中,軟硬件的深度融合已成為應(yīng)對(duì)電磁兼容挑戰(zhàn)的必然趨勢(shì)。